ZL30112

Overview

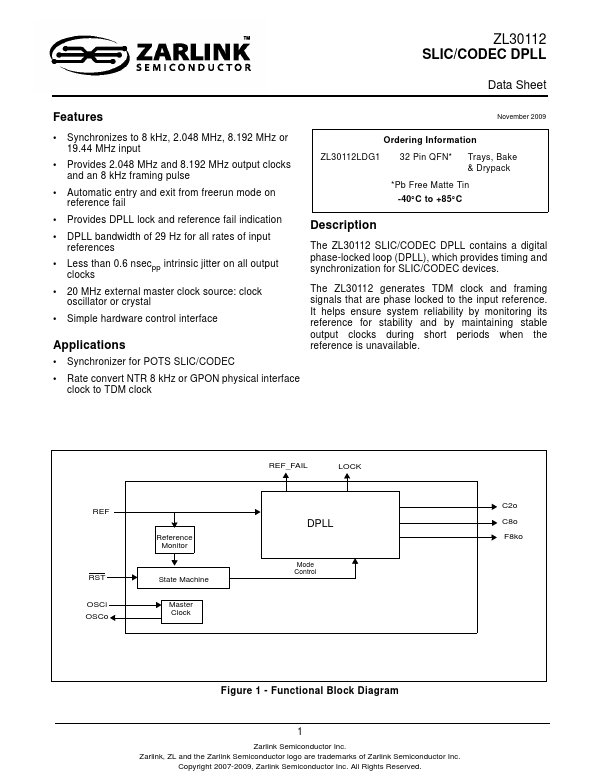

The ZL30112 SLIC/CODEC DPLL contains a digital phase-locked loop (DPLL), which provides timing and synchronization for SLIC/CODEC devices. The ZL30112 generates TDM clock and framing signals that are phase locked to the input reference.

- Synchronizes to 8 kHz, 2.048 MHz, 8.192 MHz or 19.44 MHz input

- Provides 2.048 MHz and 8.192 MHz output clocks and an 8 kHz framing pulse

- Automatic entry and exit from freerun mode on reference fail